+44 75754 30035 help@rapidassignmenthelp.co.uk

offer

🎁Special Offer 🎁 Discounts - Up to 50% OFF!

🎁Special Offer 🎁 Discounts - Up to 50% OFF!

The goal of this project is to show the design, implementation and testing of a sequential digital circuit to display the my student ID number on Altera FPGA board. Alter FPGA board used was the Altera Quartus II software with DE2-115 or the DE10-Lite. It details the methods and challenges through which the report was produced, and what was achieved as its outcome. Once the display makes the transition from basic LED to 7 segment LED scrolling, it displays different levels of achievement, pass, merit and distinction. This project focuses on building a project which includes working on FPGA programming, hardware demonstration, and sequential circuit design. They are important aspect of today’s digital system design and relate to the module’s learning objectives.

This design attempted to build a sequencial circuits that would display the student ID number on LED's and 7 segments displays, and have varying grades. The project was state machines for sequential operations and BCD encoding for display compatibility with Altera Quartus II software and the DE2-115 FPGA board (Galloway, 2022). Flip-flops and counters were configured to space and time the sequencing and components were interfaced with LEDs and 7 segment displays. To demonstrate the design, it was simulated to validate and to ensure that functional requirements were met.

The design implementation concentrated on constructing a sequential circuit using FPGA board which would show the student ID number(32054142). Thus, a state machine was built to model each digit of the ID. The transition of the system from one state to another was controlled with a clock driven counter, such that each digit was sequentially brought into view. Also, a reset function that facilitates initialization of the display was implemented so that it can be re-initialised during operation. Binary Coded Decimal (BCD) encoding was used to show the digits onto a 7 segment display. The decimal digits of the student ID's were encoded into something that would work with the 7 segment display. Additionally, multiplexing was used to allow the ID number to appear on several 7 segment displays to provide a seamless scrolling effect between displays as the ID transitioned from display to display (Gray et al., 2024). The advanced functionality met the projects higher grade requirements. The FPGA pins were configured according to the DE2-115 board’s layout. Specific pins for the 7 segment display were assigned and proper signal routing could be done on Quartus II software. To have some timed control over the timing and initialization of the circuit, the clock and reset inputs were set to be external controllable. The states of the design were stored into flip-flops used to implement sequential logic, while counters controlled the timing and speed of the state transitions.

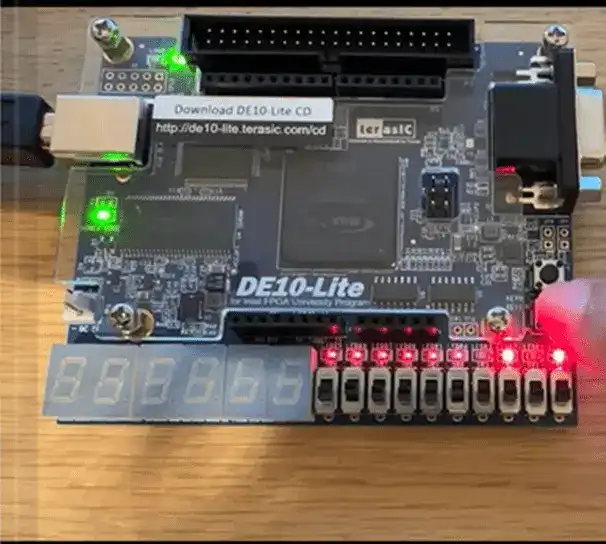

Figure 1: DE10-Lite board for hardware testing

(Source: Self-created)

The design was simulated and verified for accuracy once, was then uploaded onto the FPGA board. The final implementation showed the student ID number on LEDs by transitioning it sequentially on one 7-segment display (with smooth scrolling across several displays as well) (Bhagyaveni et al., 2022) . The project fulfilled its objectives and met pass, merit and distinction grade criteria and this implementation provided robust hardware integration.

Get assistance from our PROFESSIONAL ASSIGNMENT WRITERS to receive 100% assured AI-free and high-quality documents on time, ensuring an A+ grade in all subjects.

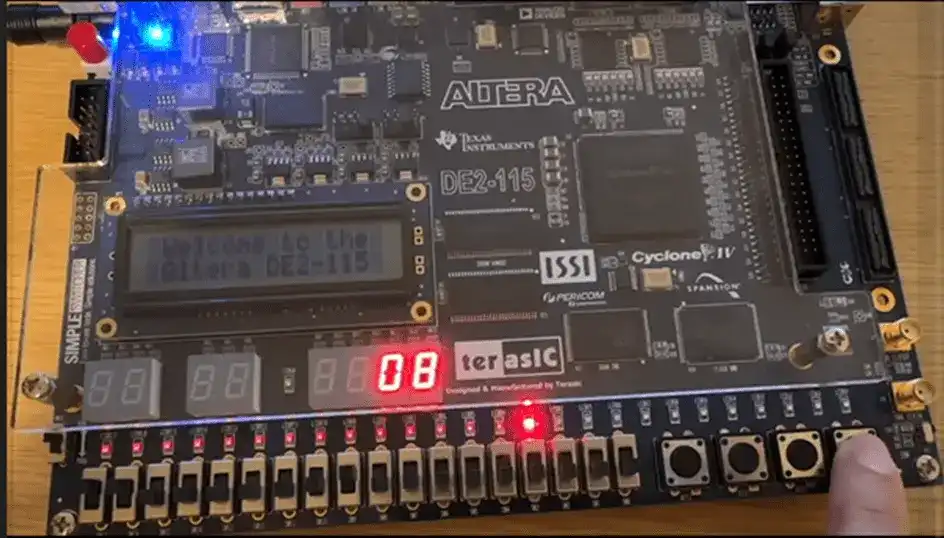

Figure 2: DE2-115 FPGA board for hardware testing

(Source: Self-created)

The design verification and evaluation, to validate by simulated for functionality, and to test out the circuit with hardware. In the beginning, Altera Quartus II software was used to sim with the sequential circuit on small registers to verify the logic and timing of the sequential circuit. This was crucial as it had to cheque state transitions, and also ensure correctness of display outputs before hardware implementation(Seo et al., 2022). The simulations show that the design essentially met the expectation under the specified condition.

After the simulation was successful, the design was migrated to the DE2-115 FPGA board for hardware testing. Outputs were closely monitored (LED and 7 segment display) to show it works physically. The design passed the criteria, as it could be used on hardware testing and show the student ID(C2054142) using the already built in LEDs. Also the merit criteria was satisfied by sequentially displaying the ID on one 7 segment LED. To satisfy the distinction criteria, further tested the design in the form of smooth scrolling across several 7 segment displays. Finally, the design operated reliably and made rapid transitions between states and displays satisfying all functional requirements. Some of the issues prevented the process from being completely verified. At first, the config of the pins was somewhat difficult until consulted manual of the FPGA board for a guidance and this resolved this issue. Timing problems cropped up as well during hardware testing, necessitating adjustment of the clock frequency and latter a reworking of the counter design. In doing so, the transitions on the display were adjusted properly to ensure synchronisation (Bansal et al., 2021). There is room for improvement looking forward. The user experience can be enhanced by introducing adjustable scrolling speed that can be adjusted to the point at which the display’s motion suits the user perfectly. Furthermore, state machine could be further optimised in resource usage, resulting in less resource usage and a more efficient and effective usage of resources.

Conclusion

This project gave some insight into how to design serial circuits and how to programme FPGAs. The design progression from simple LED display to more advanced scrolling 7 segment display, was shown to use digital design principles to satisfy functional specifications. The challenges were faced by conducting an iterative design and test, which emphasised the importance of simulation and real world validation during digital system design. Other future improvements could be to add dynamic patterns as display aesthetics, or integrate with user configurable settings.

This section presents the detailed structure of the Analogue Coursework Report, focusing on the design, performance, and implementation of an analogue-to-digital data acquisition system. Students seeking guidance or clarity on technical report writing can also explore expert support through Online Assignment Help for better academic outcomes.

The main purpose of this report has been to design an analogue to digital data acquisition system, which is converting a continuous analogue signals into discrete digital data which could be processed using digital systems. In real world applications, such as temperature monitoring, environmental sensors and embedded control systems in industrial automation, this is an essential type of system in data collection and processing processes. Interface with microcontrollers or digital processors involves the need to interface sensors that convey real world signals to a format that can be interpreted and manipulated by digital systems, and this involves the use of an Analogue-to-Digital Converter (ADC) system. The technology is being used extensively across many different sectors including automotive for engine control systems or healthcare for medical devices. These systems are important because they convert digital signals into real world phenomena such as temperature, pressure and voltages. A good selection of its components and knowledge of underlying theory for system design and signal conversion is necessary in the development of an ADC system.

The flexibility, accuracy, and economic impact of the ADC system were analysed in terms of different design options. These analysis techniques were chosen for the final design because it produced the correct digital representation with little complexity and with compatibility to other system components (Romijn et al., 2021). The ADC system consists of the point temperature sensors, an op amp and an Altera FPGA. Temperature sensors were so accurate and ADC compatible, while the operational amplifiers acted as buffers to make the analogue signals bigger for conversion (Mina et al., 2022). Due to its flexibility and quick data processing abilityuse of the FPGA. Procured the individual components (temperature sensors, op amps, FPGA) to estimate overall cost of the system but also because thermometers were cheap to found on the market. The system performance summary indicated the system to be able to accurately digitise analogue signals with minimal loss of data fidelity. The system also operated within the prescribed voltage and temperature outputs for obtaining reliable data for further processing.

After evaluating various options of signal conditioning, amplification, and conversion, the ADC system circuit design was carefully chosen. Illustrated here, put together the final circuit diagram that has an arrangement where the analogue temperature sensor output is fed into an operational amplifier for signal amplification to the ADC converter. It takes the amplified signal into another digital signal, which the FPGA can work on (Sánchez et al., 2023). The aim of the design rationale would be that the analogue signals coming in would be weak and the operational amplifier used would have sufficient gain to amplify such signals without bringing in significant noise. Due to its agility and processing power, the digital output of the ADC was chosen to be handled by the Altera FPGA. Component values were calculated using ideal theory taking into account of which the ideal equations governing operational amplifiers and ADC conversion were used to derive expected performance.

ORCAD PSpice simulations were performed for designed circuit for designing to predict the performance of it. In these simulations these op-amps, namely the uA741, were used because they are well studied in the world of analogue signal amplification. The practical results resulting from actual circuit implementation are compared with the simulation results for presentation and accuracy in the design (Huang et al., 2021). Input temperature values were inputted into the theoretical calculations with characteristics of the sensor and gain from the amplifier, to derive voltage values. Results demonstrated that an ADC could convert the analogue signals with minimal error, thereby achieving the required signal fidelity. Results presented in practise also appeared to support the theoretical expectations for the chosen components and design.

The ADC data implementation of the system was consistent with expected results — these voltage and temperature data. The obtained temperature values were analysed to assess the accuracy and reliability of the system under varied conditions. The ADC was responsible of processing data coming from the temperature sensors and converting them into digital values. These resultant data were cross checked against the known reference values, and the system performance was evaluated (Pavlidis et al., 2021). Overall, the system was accurate (within the test margin of error), and obtained results that were close to what expected in terms of deviation (except for some small deviations owing to real world imperfections (component tolerances) or external factors (noise interference)). However, with these variations, the overall system effectiveness in providing reliable temperature data for a variety of applications was not affected as the effectiveness was still outstanding. Conversion of analogue signals to digital data was demonstrated by the design results to be effective with signal conditioning to provide high quality conversions.

Additionally, the analysis of the system effectiveness showed that the use of the operational amplifier for signal conditioned has great impact on the quality of the signal going into the ADC. In fact, these temperature readings were greatly enhanced in accuracy with a use of an amplifier with gain best adjusted to match the levels of input signal (Loke et al., 2021). This finding calls attention to the importance of being careful and selective when choosing components and, of ensuring that proper testing and validation is completed to be confident in system reliability.

Conclusion

An analogue to digital data acquisition system is presented for converting analogue temperature signals into digital data. Great care went into translating concepts into an engineering reality and the selection of components with an eye towards performance requirements. Theoretical calculations and practical tests showed that the system worked as expected in the performance evaluation. However, minor discrepancies were noted because of real world factors, but the system had good accuracy. Future work, in which improvements to the signal conditioning circuit are likely, and improvements to ADC architectures for high precision as well as addressing error sources are possible. This also serves as a reminder that component selection and that system performance must be simulated and tested both, are inescapable parts of this development.

Reference List

Journal

Introduction Get Free Online Assignment Samples from UK's Best Assignment Help Experts to boost your academic...View and Download

Introduction to People Management Assignment PART1 1.1 Evaluation of the concept The concept of evidence-based approaches...View and Download

1. Introduction to Epidemiology of Communicable and Non-Communicable Diseases Assignment Sample Tuberculosis (TB) is an...View and Download

Introduction Get free samples written by our Top-Notch subject experts for taking online Assignment Help services. Foreign...View and Download

Introduction: COVID-19 and the UK Auto Industry Shift The worldwide spread of COVID-19 has altogether influenced different...View and Download

Introduction: Sustainable Operations Management Get free samples written by our Top-Notch subject experts for taking Online...View and Download